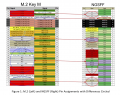

M.2 Pins

M.2 pinout for key B (1x SATA, 2x PCIe)

Pin Number Pin Name Description

- 1 CONFIG_3 Defines module type

- 2 3.3 V Supply pin, 3.3 V

- 3 GND Ground

- 4 3.3 V Supply pin, 3.3 V

- 5 N/C

- 6-8 N/A

- 9 N/C

- 10 DAS/DSS Device Activity Signal / Disable Staggered Spinup

- 11 N/C

- 12-19 removed Mechanical notch B

- 20 N/A

- 21 CONFIG_0 Defines module type

- 22-26 N/A

- 27 GND Ground

- 28 N/A

- 29 PERn1 / USB TX- PCIe Lane 1 Rx or USB 3.0 TX-

- 30 N/A

- 31 PERp1 / USB TX+ PCIe Lane 1 Rx or USB 3.0 TX+

- 32 N/A

- 33 GND Ground

- 34 N/A

- 35 PETn1 / USB RX- PCIe Lane 1 Tx or USB 3.0 RX-

- 36 N/A

- 37 PETp1 / USB RX+ PCIe Lane 1 Tx or USB 3.0 RX+

- 38 DEVSLP Device Sleep, input. If driven high the host is informing the SSD to enter a low power state.

- 39 GND Ground

- 40 N/A

- 41 SATA-B+/PERn0 Host receiver differential signal pair. If in PCIe mode PCIe Lane 0 Rx

- 42 N/A

- 43 SATA-B-/PERp0 Host receiver differential signal pair. If in PCIe mode PCIe Lane 0 Rx

- 44 N/A

- 45 GND Ground

- 46 N/A

- 47 SATA-A-/PETn0 Host transmitter differential signal pair. If in PCIe mode PCIe Lane 0 Tx

- 48 N/A

- 49 SATA-A+/PETp0 Host transmitter differential signal pair. If in PCIe mode PCIe Lane 0 Tx

- 50 PERST# PCIe reset

- 51 GND Ground

- 52 CLKREQ# Reference clock request signal

- 53 REFCLKN PCIe Reference Clock signals (100 MHz)

- 54 PEWAKE# PCIe WAKE# Open Drain with pull up on platform. Active Low.

- 55 REFCLKP PCIe Reference Clock signals (100 MHz)

- 56 MFG1 Manufacturing pin. Use determined by vendor.

- 57 GND Ground

- 58 MFG2 Manufacturing pin. Use determined by vendor.

- 59-66 removed Mechanical notch M

- 67 N/A

- 68 SUSCLK 32.768 kHz clock supply input provided by the Platform chipset

- 69 CONFIG_1 Defines module type

- 70 3.3 V Supply pin, 3.3 V

- 71 GND Ground

- 72 3.3 V Supply pin, 3.3 V

- 73 GND Ground

- 74 3.3 V Supply pin, 3.3 V

- 75 CONFIG_2 Defines module type

M.2 pinout for key M (1x SATA, 1x, 2x, or 4x PCIe)

Pin Number Pin Name Description

- 1 CONFIG_3 Defines module type

- 2 3.3 V Supply pin, 3.3 V

- 3 GND Ground

- 4 3.3 V Supply pin, 3.3 V

- 5 PERn3 PCIe Lane 3 Rx

- 6 N/A

- 7 PERp3 PCIe Lane 3 Rx

- 8 N/A

- 9 GND Ground

- 10 DAS/DSS Device Activity Signal / Disable Staggered Spinup

- 11 PETn3 PCIe Lane 3 Tx

- 12 3.3 V Supply pin, 3.3 V

- 13 PETp3 PCIe Lane 3 Tx

- 14 3.3 V Supply pin, 3.3 V

- 15 GND Ground

- 16 3.3V Supply pin, 3.3 V

- 17 PERn2 PCIe Lane 2 Rx

- 18 3.3 V Supply pin, 3.3 V

- 19 PERp2 PCIe Lane 2 Rx

- 20 N/A

- 21 CONFIG_0 Defines module type

- 22 N/A

- 23 PETn2 PCIe Lane 2 Tx

- 24 N/A

- 25 PETp2 PCIe Lane 2 Tx

- 26 N/A

- 27 GND Ground

- 28 N/A

- 29 PERn1 PCIe Lane 1 Rx

- 30 N/A

- 31 PERp1 PCIe Lane 1 Rx

- 32 N/A

- 33 GND Ground

- 34 N/A

- 35 PETn1 PCIe Lane 1 Tx

- 36 N/A

- 37 PETp1 PCIe Lane 1 Tx

- 38 DEVSLP Device Sleep, input. If driven high the host is informing the

- SSD to enter a low power state.

- 39 GND Ground

- 40 N/A

- 41 SATA-B+/PERn0 Host receiver differential signal pair. If in PCIe mode PCIe Lane 0 Rx

- 42 N/A

- 43 SATA-B-/PERp0 Host receiver differential signal pair. If in PCIe mode PCIe Lane 0 Rx

- 44 N/A

- 45 GND Ground

- 46 N/A

- 47 SATA-A-/PETn0 Host transmitter differential signal pair. If in PCIe mode PCIe Lane 0 Tx

- 48 N/A

- 49 SATA-A+/PETp0 Host transmitter differential signal pair. If in PCIe mode PCIe Lane 0 Tx

- 50 PERST# PCIe reset

- 51 GND Ground

- 52 CLKREQ# Reference clock request signal

- 53 REFCLKN PCIe Reference Clock signals (100 MHz)

- 54 PEWAKE# PCIe WAKE# Open Drain with pull up on platform. Active Low.

- 55 REFCLKP PCIe Reference Clock signals (100 MHz)

- 56 MFG1 Manufacturing pin. Use determined by vendor.

- 57 GND Ground

- 58 MFG2 Manufacturing pin. Use determined by vendor.

- 59-66 removed Mechanical notch M

- 67 N/A

- 68 SUSCLK 32.768 kHz clock supply input provided by the Platform chipset

- 69 CONFIG_1 Defines module type

- 70 3.3 V Supply pin, 3.3 V

- 71 GND Ground

- 72 3.3 V Supply pin, 3.3 V

- 73 GND Ground

- 74 3.3 V Supply pin, 3.3 V

- 75 CONFIG_2 Defines module type

M.2 Key A

M.2 Key E

M.2 dual module key A and E

Pin id. Pin name Description

- 1 GND Ground

- 2 +3.3V 3.3 V power supply

- 3 USB_D+ USB high-, full-, and low- speed data pair positive

- 4 +3.3V 3.3 V power supply

- 5 USB_D- USB high-, full-, and low- speed data pair negative

- 6 LED1#

- 7 GND Ground

- 8 Key Substrate removed to act as physical key

- 9 Key Substrate removed to act as physical key

- 10 Key Substrate removed to act as physical key

- 11 Key Substrate removed to act as physical key

- 12 Key Substrate removed to act as physical key

- 13 Key Substrate removed to act as physical key

- 14 Key Substrate removed to act as physical key

- 15 Key Substrate removed to act as physical key

- 16 LED2#

- 17 DNC Do not connect

- 18 GND Ground

- 19 DNC Do not connect

- 20 DNC Do not connect

- 21 DNC Do not connect

- 22 DNC Do not connect

- 23 Key Substrate removed to act as physical key

- 24 Key Substrate removed to act as physical key

- 25 Key Substrate removed to act as physical key

- 26 Key Substrate removed to act as physical key

- 27 Key Substrate removed to act as physical key

- 28 Key Substrate removed to act as physical key

- 29 Key Substrate removed to act as physical key

- 30 Key Substrate removed to act as physical key

- 31 Key Substrate removed to act as physical key

- 32 DNC Do not connect

- 33 GND Ground

- 34 DNC Do not connect

- 35 PETp0 PCI Express lane 0 module transmitter pair positive

- 36 DNC Do not connect

- 37 PETn0 PCI Express lane 0 module transmitter pair negative

- 38 Vendor defined

- 39 GND Ground

- 40 Vendor defined

- 41 PERp0 PCI Express lane 0 module receiver pair positive

- 42 Vendor defined

- 43 PERn0 PCI Express lane 0 module receiver pair negative

- 44 COEX3 Antenna coexistence signal 3

- 45 GND Ground

- 46 COEX2 Antenna coexistence signal 2

- 47 PEFCLKP0 PCI Express reference clock pair positive

- 48 COEX1 Antenna coexistence signal 1

- 49 PEFCLKN0 PCI Express reference clock pair negative

- 50 SUSCLK 32.768 kHz clock module input

- 51 GND Ground

- 52 PERST0# PCI Express reset

- 53 CLKREQ0# PCI Express clock request

- 54 W_DISABLE2# Wireless disable 2

- 55 PEWake0# PCI Express wake

- 56 W_DISABLE1# Wireless disable 1

- 57 GND Ground

- 58 SMB_DATA SMBus data signal

- 59 Reserved

- 60 SMB_CLK SMBus clock signal

- 61 Reserved

- 62 ALERT# SMBus alert signal

- 63 GND Ground

- 64 Reserved

- 65 Reserved

- 66 UIM_SWP

- 67 Reserved

- 68 UIM_POWER_SNK

- 69 GND Ground

- 70 UIM_POWER_SRC

- 71 Reserved

- 72 +3.3V 3.3 V power supply

- 73 Reserved

- 74 +3.3V 3.3 V power supply

- 75 GND Ground